http://www.treeos.com

## 关于 PL2303 电平转换芯片模块的技术文档

## 一、产品简介

PL-2303 是连接 USB 和标准 RS232 串口的芯片,在这个芯片上的数据缓存融合了两个不同的数据流,USB 批量数据类型适应最大数据传输方式,串口支持自动握手功能,这样与传统的 UART 控制器相比,能达到很高的波特率。

此控制芯片同样也适用 USB 电源管理和远程唤醒功能。使其在挂起是达到功耗最低,SOIC-28 这种封装集成了所有的功能,这样此芯片适用潜入。适用者只要将芯片挂在电脑或 USB 端口即可以连接 RS-232 设备。

#### 引脚描述:

| 标号 | 名称      | 类型  | 说明                                                                                                                                          |

|----|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | TXD     | 0   | 串口数据输出端口                                                                                                                                    |

| 2  | DTR_N   | 0   | 数据终端就绪,低电平有效                                                                                                                                |

| 3  | RTS_N   | 0   | 请求发送,地电平有效                                                                                                                                  |

| 4  | VDD_232 | P   | RS232 的电源。RS232 的输出信号(1-3 脚)被设置成 5V,<br>3. 3V 和 3V。VDD_232 的电压应当和 RS232 的电压相同。<br>(RS232 的输入信号总是被设置在 5V-3V 之间)。<br>注意:此版本仅提供 5V 信号。但将来可能回升级 |

| 5  | RXD     | I   | 串行数据输入                                                                                                                                      |

| 6  | RI_N    | I   | 振铃指示                                                                                                                                        |

| 7  | GND     | P   | 地                                                                                                                                           |

| 8  | VDD     | P   | 电源                                                                                                                                          |

| 9  | DSR_N   | I   | 数据设置就绪,低电平有效                                                                                                                                |

| 10 | DCD_N   | I   | 数据载波检测,低电平有效                                                                                                                                |

| 11 | CTS_N   | I   | 清除发送,低电平有效                                                                                                                                  |

| 12 | SHTD_N  | 0   | 关闭 RS232 收发                                                                                                                                 |

| 13 | EE_CLK  | I/0 | 当复位时,此引脚用于输入模拟信号,在正常状态下,此引脚为串行 ROM 时钟                                                                                                       |

| 14 | EE_DATA | I/0 | ROM 串行数据信号                                                                                                                                  |

#### http://www.treeos.com

| 15 | DP         | I/0 | USB 的 DPLUS 信号                  |

|----|------------|-----|---------------------------------|

| 16 | DM         | I/0 | USB 的 DMINUS 信号                 |

| 17 | VDD_3V3    | P   | 提供给 USB 发送的 3.3V 电源             |

| 18 | GND_3V3    | P   | 3.3V 地                          |

| 19 | RESET      | I   | 系统复位引脚                          |

| 20 | VDD        | P   | 电源                              |

| 21 | GND        | P   | 地                               |

| 22 | RTI_STATE  | I   | 该引脚在复位后涉及到                      |

|    | 9333       |     | 高电平: RS-232 在挂起时此引脚输出无效         |

|    |            |     | 低电平: RS-232 在挂起时此引脚处于三态状态       |

| 23 | LD_MD/SHTD | I/0 | 下载模式/SHTD                       |

|    | 500        |     | 此引脚在复位时为输入。需加上拉电阻(220K)用来防止     |

|    |            |     | USB产生过流(500mA)现象。加下拉电阻(220K)防止电 |

|    |            |     | 流过低 (100mA)。                    |

|    |            |     | 复位后,此引脚变成输出,它地输出正好和 SHRTD_N 相反。 |

| 24 | VDD_PLL    | P   | PLL 5V 电源                       |

| 25 | GND_PLL    | P   | PLL 地                           |

| 26 | PLL_TEST   | I   | PLL 测试模式控制                      |

| 27 | 0SC1       | I   | 晶振輸入                            |

| 28 | OSC2       | 0   | 晶振输出                            |

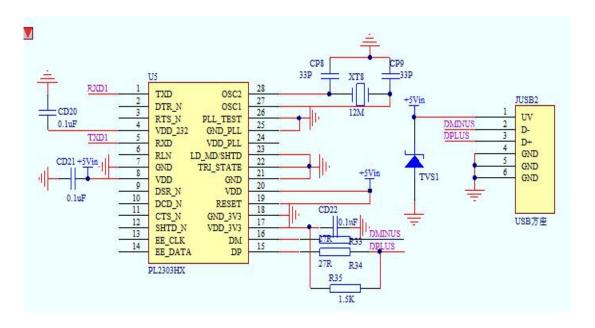

# 二、硬件调试

(1)、硬件实物图展示如下图:

http://www.treeos.com

(2)、模块原理图接口展示如图:

(3)单片机管脚链接表: 详见收到的 AD 工程中的 Device For Communication中的 PL2303 模块原理图。

http://www.treeos.com

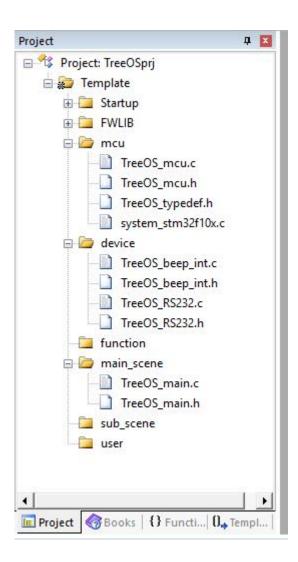

## 三、软件调试

本案例基于光轮电子公司 TreeOS 架构运行,具体软件工程还请关注光轮电子公司 TreeOS 驱动库文件。